# Electrical properties of ZnO nanowire field effect transistors with varying high- $k \operatorname{Al}_2O_3$ dielectric thickness

Minhyeok Choe, Gunho Jo, Jongsun Maeng, Woong-Ki Hong, Minseok Jo, Gunuk Wang, Woojin Park, Byoung Hun Lee, Hyunsang Hwang, and Takhee Lee<sup>a)</sup> Department of Nanobio Materials and Electronics, Department of Materials Science and Engineering, Gwangju Institute of Science and Technology, Gwangju 500-712, Republic of Korea

(Received 30 December 2009; accepted 4 January 2010; published online 5 February 2010)

We investigated the electronic properties of ZnO nanowire combined with the scaled high-k Al<sub>2</sub>O<sub>3</sub> dielectrics using metal-oxide-semiconductor and field effect transistor (FET) device structures. We found that Al<sub>2</sub>O<sub>3</sub> dielectric material can significantly reduce leakage currents when the applied voltage was restricted less than the transition voltage of direct tunneling to Fowler–Nordheim tunneling. The ZnO nanowire FETs with Al<sub>2</sub>O<sub>3</sub> dielectrics exhibited the increase in electrical conductance, transconductance, and mobility and the threshold voltage shifted to the negative gate bias direction with decreasing Al<sub>2</sub>O<sub>3</sub> dielectric layer thickness. © 2010 American Institute of Physics. [doi:10.1063/1.3298910]

### **I. INTRODUCTION**

Continuous miniaturization, such as physical channel length and gate dielectric thickness down to the nanometer scale, is becoming increasingly difficult in semiconductor technology due to limitations of fundamental physics such as tunneling leakage problem of ultrathin gate oxides used in metal-oxide-semiconductor (MOS) transistors.<sup>1-5</sup> To overcome this unavoidable problems, new device structures and material approaches have been proposed. For example, field effect transistors (FETs) based on nanowires and carbon nanotubes have been intensively investigated. These onedimensional nanostructures have provided new challenges in terms of the controlled growth of nanoscale wire diameter and patterning processes at the nanometer scale.<sup>6</sup> In addition, the high-k dielectric materials including  $Al_2O_3$ ,  $Y_2O_3$ ,  $ZrO_2$ , and HfO<sub>2</sub> have been attractive due to its good surface adhesion, high capacitance, and thermal and chemical stability while reducing direct-tunneling leakage currents.<sup>2–5</sup>

In particular, the FET devices using nanostructures have been investigated using bottom-gate structure with a SiO<sub>2</sub> dielectric layer. However, as the SiO<sub>2</sub> dielectrics become thinner, the leakage current increases dramatically due to the quantum-mechanical tunneling effect through the dielectric layer.<sup>5,7</sup> Therefore, recently, the electrical properties of FETs based on semiconductor nanowires and carbon nanotubes combined with high-*k* gate dielectrics have been investigated.<sup>8,9</sup> For example, Javey *et al.*<sup>8</sup> reported integrating high-*k* dielectrics into carbon-nanotube transistors, which exhibited high transconductance and mobility without serious gate leakage current. And, logic circuits were successfully demonstrated using ZnO nanowire FETs with high-*k* dielectrics.<sup>9</sup>

Since a reduction in channel length accompanies diminishing oxide dielectric thickness, nanowire or nanotube FETs with high-k dielectrics are of great interest for potentially shrinking the device structures. Particularly, the leakage characteristics need to be thoroughly analyzed in a wide range of voltage, both below and above the transition voltage at which the leakage conduction is changed from direct tunneling (DT) to Fowler–Nordheim (FN) (or called as field emission) tunneling. In this work, we report on the electrical characteristics of ZnO nanowire FETs with Al<sub>2</sub>O<sub>3</sub> dielectric layers. We have characterized the tunneling leakage current of the Al<sub>2</sub>O<sub>3</sub> layers with different thickness in terms of the tunneling conduction mechanisms, and have investigated the electrical properties of the ZnO nanowire FETs with scaled Al<sub>2</sub>O<sub>3</sub> dielectric layer.

#### **II. EXPERIMENTAL SECTION**

# A. Fabrication of MOS structure with Al<sub>2</sub>O<sub>3</sub> dielectric layer

The high-k Al<sub>2</sub>O<sub>3</sub> layer used in this study was deposited by atomic layer deposition onto two types of substrates; a *p*-type silicon substrate and a heavily doped *p*-type silicon substrate. The *p*-type silicon substrate was used to fabricate the MOS structure [see inset of Fig. 1(a)] for extracting the dielectric constant of Al<sub>2</sub>O<sub>3</sub> layer, whereas the heavily doped *p*-type silicon substrate was used to analyze tunneling characteristics of Al<sub>2</sub>O<sub>3</sub> layer and to fabricate ZnO nanowire FETs. The Al<sub>2</sub>O<sub>3</sub> layer was intended to grow to 20, 50, and

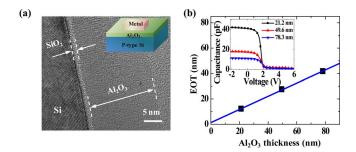

FIG. 1. (Color online) (a) HRTEM image of  $Al_2O_3$  dielectric layer (21.2 nm). The inset shows schematic of a MOS device structure. (b) EOT vs thickness of  $Al_2O_3$  dielectric layer. The inset shows a series of C-V characteristics.

0021-8979/2010/107(3)/034504/4/\$30.00

107, 034504-1

<sup>&</sup>lt;sup>a)</sup>Electronic mail: tlee@gist.ac.kr.

80 nm thick, but the actual physical thickness of  $Al_2O_3$  layer was found to be ~19.7, 48.1, and 76.8 nm, respectively, when measured with a variable angle spectroscopic ellipsometer.

To reduce the oxygen vacancy in Al<sub>2</sub>O<sub>3</sub> layer, the post deposition annealing (PDA) was carried out at 800 °C for 1 min at oxygen ambient. The PDA process was meant to enhance the stoichiometry of Al<sub>2</sub>O<sub>3</sub> by reducing the oxygen vacancy and thus reducing the trap-assisted leakage currents.<sup>10</sup> An interfacial SiO<sub>2</sub> layer was also formed during the PDA process. The thickness of this interfacial SiO<sub>2</sub> layer was estimated as ~1.54 nm from the high resolution transmission electron microscopy (HRTEM) image in Fig. 1(a). Henceforth we refer to the Al<sub>2</sub>O<sub>3</sub> layer thickness as the sum of the deposited Al<sub>2</sub>O<sub>3</sub> layer and the interfacial SiO<sub>2</sub> layer thickness (~21.2, 49.6, and 78.3 nm). This interfacial SiO<sub>2</sub> layer can be formed naturally in the ambient air, and also can be formed by oxygen in the Al<sub>2</sub>O<sub>3</sub> layer during the PDA process.<sup>11</sup>

After PDA process, metal electrode layers were deposited by an electron beam evaporator and defined as the junction electrode by using a photolithography and lift-off process. The capacitance-voltage (C-V) was measured by the MOS devices at 1.0 MHz frequency conditions at room temperature with  $Al_2O_3$  dielectric layers grown on a *p*-type silicon. And, the leakage current-voltage was measured by the MOS devices with  $Al_2O_3$  and SiO<sub>2</sub> dielectric layers grown on a heavily doped *p*-type silicon substrate using a semiconductor parameter analyzer (Agilent B1500A).

#### B. Fabrication of ZnO nanowire field effect transistors

We investigated the electrical properties of ZnO nanowire FETs with  $Al_2O_3$  dielectric layers with the same three different thicknesses (21.2, 49.6, and 78.3 nm) as the MOS structure devices. For this purpose, the ZnO nanowires were grown via a vapor transport method on *c*-plane sapphire substrate coated with a thin Au film which acts as a catalyst for ZnO nanowire growth. The diameters of the ZnO nanowires were found to be  $100.4 \pm 12.2$  nm, statistically determined from the field emission scanning electron microscopy (FESEM) images of ~100 different nanowires. This ZnO nanowire synthesis method has been explained in detail elsewhere.<sup>12</sup>

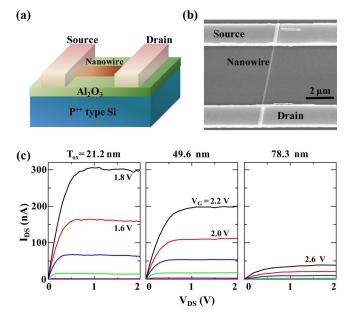

To fabricate ZnO nanowire FETs, the grown ZnO nanowires were transferred to Al<sub>2</sub>O<sub>3</sub>/Si (heavily doped *p*-type) substrate from the sapphire substrate. The heavily doped *p*-type silicon substrate acts as a back-gate electrode [see Fig. 2(a)]. Then source and drain electrodes (gap of  $3-4 \mu$ m) are formed by using photolithography and lift-off process [see Fig. 2(b)]. The current-voltage characteristics of the ZnO nanowire FETs were measured using a semiconductor parameter analyzer (Agilent B1500A) at room temperature and restricted in a voltage range less than 3 V due to the FN tunneling current.

FIG. 2. (Color online) (a) Schematic of a ZnO nanowire FET device structure. (b) Scanning electron microscopy image of a single ZnO nanowire connected between source and drain electrodes in a FET device. (c) A series of  $I_{DS}-V_{DS}$  characteristics for ZnO nanowire FETs with varying  $Al_2O_3$  dielectric thicknesses (21.2, 49.6, and 78.3 nm).

#### **III. RESULTS AND DISCUSSION**

## A. Analysis of high-k Al<sub>2</sub>O<sub>3</sub> dielectrics

Figure 1(a) shows the cross-sectional HRTEM image of 21.2 nm thick  $Al_2O_3$  dielectric layer and the insert shows schematic of a MOS device structure. An interfacial SiO<sub>2</sub> layer and an  $Al_2O_3$  layer were clearly distinct in this figure. From C-V measurements with MOS structure, the equivalent oxide thickness (EOT) was calculated using an NCSU CVC program, which is an analysis program used to extract thin oxide parameters.<sup>13</sup> It is from the EOT as a function of the  $Al_2O_3$  layer thickness are extracted. The plot in Fig. 1(b) represents the function

$$EOT = \frac{k_{SiO_2}}{k_{Al_2O_3}} t_{Al_2O_3} + t_{SiO_2},$$

(1)

where  $k_{SiO_2}$  and  $k_{Al_2O_3}$  are the dielectric constants for  $Al_2O_3$ and SiO<sub>2</sub>, respectively,  $t_{Al_2O_3}$  is the Al<sub>2</sub>O<sub>3</sub> thickness, and  $t_{SiO_2}$ is the thickness of the SiO<sub>2</sub> interfacial layer. The slope of this plot yields an Al<sub>2</sub>O<sub>3</sub> dielectric constant of ~7.55, and the *y*-intercept of the plot reveals the SiO<sub>2</sub> interfacial layer thickness to be ~1.46 nm. The dielectric constant of the Al<sub>2</sub>O<sub>3</sub> layer has been reported in the range of 7–10, and it seems to depend on detailed growth conditions such as deposition process, growth temperature, precursor gas, and annealing treatment.<sup>14–16</sup> The interfacial SiO<sub>2</sub> layer thickness (~1.46 nm) extracted from the EOT versus the Al<sub>2</sub>O<sub>3</sub> layer thickness [Fig. 1(b)] is consistent with the observed interfacial SiO<sub>2</sub> layer thickness (~1.54 nm) from HRTEM image.

The key advantage of using  $Al_2O_3$  dielectrics is the reduction in leakage current compared to  $SiO_2$  dielectrics with equal EOT values. Figure 3(a) displays the leakage current density versus applied voltage, measured from MOS struc-

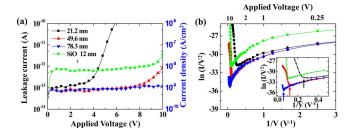

FIG. 3. (Color online) (a) Leakage current density vs applied voltage through  $Al_2O_3$  dielectric layers of different thicknesses (21.2, 49.6, and 78.3 nm) and a 12 nm SiO<sub>2</sub> layer. (b)  $ln(I/V^2)$  vs 1/V plot for  $Al_2O_3$  and 12 nm SiO<sub>2</sub> dielectric layers. Inset is a zoomed-in plot near the transition voltages (marked by arrows) from DT to FN tunneling (see text in detail).

ture devices with Al<sub>2</sub>O<sub>3</sub> dielectric layers (thicknesses of 21.2, 49.6, and 78.3 nm) and  $SiO_2$  layer (12 nm thick). The SiO<sub>2</sub> layer thickness of 12 nm was chosen for comparison because the EOT value of the 21.2 nm thick Al<sub>2</sub>O<sub>3</sub> layer was determined as 12 nm from Eq. (1). This leakage current is the sum of the quantum-mechanical tunneling current through the dielectric layers and the charging current associated with the capacitance values of the dielectric layers. As shown in Fig. 3(a), the leakage current was shown to decrease with increasing thickness of the Al<sub>2</sub>O<sub>3</sub> layer. The leakage current density for the Al<sub>2</sub>O<sub>3</sub> layers was very low on the order of  $1 \text{ nA/cm}^2$  when the applied bias was not too high, indicating the excellent insulating behavior of Al<sub>2</sub>O<sub>3</sub> dielectric layers. Groner et al. also reported that the leakage current for Al<sub>2</sub>O<sub>3</sub> layers of thickness between 3 and 115 nm was in the range of 10 to 0.1  $nA/cm^{2.5}$  As shown in Fig. 3(a), the observed leakage current for the 12 nm SiO<sub>2</sub> layer  $(\sim 10 \text{ nA/cm}^2)$  was about ten times higher than that of the 21.2 nm Al<sub>2</sub>O<sub>3</sub> layer ( $\sim 1 \text{ nA/cm}^2$ ) when the applied bias was less than 4 V. At above 4 V, the leakage current for the 21.2 nm Al<sub>2</sub>O<sub>3</sub> layer increased dramatically more than that for the 12 nm  $SiO_2$  layer. This behavior can be explained by FN tunneling through the dielectric layer. When the applied bias is less than the barrier height of an insulating dielectric layer, DT occurs, whereas when the applied bias is higher than the barrier height, FN tunneling occurs.

In order to analyze the tunneling characteristics, we investigated the transition of DT to FN tunneling for all three  $Al_2O_3$  layers (21.2, 49.6, and 78.3 nm thick) and the SiO<sub>2</sub> layer (12 nm thick), as shown in Fig. 3(b). Beebe *et al.*<sup>17</sup> reported that a plot of  $\ln(I/V^2)$  versus 1/V exhibits logarithmic growth when the applied bias is less than the barrier height in the DT regime, whereas this plot exhibits a linear decay when the applied bias is higher than the barrier height in the FN tunneling regime. The transition from DT to FN tunneling accompanies a change in the barrier shape from trapezoidal to triangular, and it appears as an inflection in the plot of  $\ln(I/V^2)$  versus 1/V.<sup>17</sup> Thus, the transition voltage provides a means of experimentally estimating the height of the original rectangular barrier. The inflection point (i.e., the barrier height) was observed to decrease as the thickness of the  $Al_2O_3$  dielectric layer was decreased [Fig. 3(b)]. This behavior is clearly seen in the zoomed-in plot near the transition voltages [the inset of Fig. 3(b)]. Specifically, the transition voltage was observed as  $\sim$ 3.4, 7.6, and 13.6 V for

21.2, 49.6, and 78.3 nm thick Al<sub>2</sub>O<sub>3</sub> dielectric layers, respectively. For the 12 nm SiO<sub>2</sub> case, the transition voltage was observed to be ~8.6 V. FN tunneling at relatively small bias (~3.4 V) for the 21.2 nm thick Al<sub>2</sub>O<sub>3</sub> dielectric layer explains the dramatic increase in leakage current above ~3.4 V, as well as the fact that its leakage current is higher than that of the 12 nm SiO<sub>2</sub> layer above ~4 V [Fig. 3(a)]. Note that Ng *et al.*,<sup>18</sup> reported a similar trend of barrier height dependence on the thickness of SiO<sub>x</sub>N gate dielectric layer.

#### B. Electrical properties of ZnO nanowire transistors

The ZnO nanowire FETs with high-k Al<sub>2</sub>O<sub>3</sub> dielectric layers (thicknesses of 21.2, 49.6, and 78.3 nm) were fabricated to investigate their electrical properties. The FET device schematic and FESEM image of a fabricated device are shown in Figs. 2(a) and 2(b), respectively. During the electrical measurements, the current-voltage characteristics of the ZnO nanowire FETs were restricted in a voltage range less than 3 V, since FN tunneling current in MOS devices with 21.2, 49.6, and 78.3 nm thick Al<sub>2</sub>O<sub>3</sub> and 12 nm SiO<sub>2</sub> dielectric layers is negligible below 3 V [Fig. 3(b)]. Figure 2(c) shows a series of source-drain current versus drain voltage (I<sub>DS</sub>-V<sub>DS</sub>) characteristics of the ZnO nanowire FETs with Al<sub>2</sub>O<sub>3</sub> dielectric layers. In all cases, the I<sub>DS</sub>-V<sub>DS</sub> curves exhibited well-defined linear regimes at low bias levels and saturation regimes at high bias levels. This is typical electrical behavior for *n*-type FETs. The gate bias for on-current state is dependent on the dielectric layer thickness. As the dielectric layer thickness decreased, the current increased. This trend is due to the increased carrier modulation efficiency by the gate bias through the thinner dielectric layer. In other words, a higher gate bias is needed in nanowire FETs with a thicker dielectric layer to maintain the on-current state.

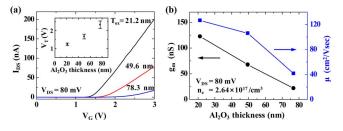

Figure 4(a) displays the source-drain current versus the gate voltage ( $I_{DS}$ - $V_G$ ) characteristics of ZnO nanowire FETs with  $Al_2O_3$  dielectric layers, measured at a fixed drain bias of 80 mV. The dispersion of the threshold voltage ( $V_T$ ) values was obtained by taking statistical averages and standard deviations of sets of individual nanowire FETs (three to five FET devices at each data point), as summarized in the inset of Fig. 4(a). The  $V_T$  value decreased as the dielectric layer thickness decreased, indicating a successful gate modulation. Specifically, we observed  $V_T$  values of  $1.2 \pm 0.1$ ,  $1.7 \pm 0.1$ ,

FIG. 4. (Color online) (a)  $I_{DS}-V_G$  characteristics for ZnO nanowire FETs with varying  $Al_2O_3$  dielectric thicknesses at fixed  $V_{DS}$ =80 mV. The inset shows the statistical distribution of the measured threshold voltage. (b) Transconductance ( $g_m$ ) and mobility ( $\mu$ ) of ZnO nanowire FETs with varying  $Al_2O_3$  dielectric thicknesses.

and  $2.3 \pm 0.2$  V for ZnO nanowire FETs with dielectric layer thicknesses of 21.2, 49.6, and 78.3 nm, respectively. The  $V_{\rm T}$ values are influenced by several factors, such as the dielectric material, various charges and traps in the dielectric, the substrate doping conditions, and the device dimensions.<sup>19</sup> In our study, the increase in dielectric thickness resulted in a  $V_{\rm T}$ shift to the positive gate bias direction. This means that a higher gate bias is needed to turn on the nanowire FET with a thicker dielectric layer.

Figure 4(b) shows the transconductance  $(g_m=dI_{DS}/dV_G)$  and mobility ( $\mu$ ) for ZnO nanowire FETs with  $AI_2O_3$  dielectric layers. Mobility of ZnO nanowire FETs can be calculated from the equation

$$\mu = \frac{g_m L^2}{V_{DS} C_G},\tag{2}$$

where L is the nanowire channel length (~4  $\mu$ m), and C<sub>G</sub> is the gate capacitance. Here,  $C_G$  can be estimated from the model of a cylinder on an infinite metal plate,<sup>20</sup>  $C_G$ = $2\pi\varepsilon_0\varepsilon_r L/\cosh^{-1}(1+T_{OX}/r)$ ; herein, r is the nanowire radius (~50 nm),  $T_{OX}$  is the dielectric thickness (21.2, 49.6, and 78.3 nm),  $\varepsilon_0$  is the permittivity of free space, and  $\varepsilon_r$  $(=k_{Al_2O_2})$  is the dielectric constant of  $Al_2O_3$  [7.55 determined from Fig. 1(b)]. We calculated the mobility at the equal carrier concentration ( $\sim 2.64 \times 10^{17}$  cm<sup>-3</sup>) in ZnO nanowire FETs with different dielectric layer thicknesses, since the scattering is susceptible to carrier concentration and surface roughness. With this reason, the transconductance for calculating mobility was extracted from the gate voltage at an equal carrier concentration ( $\sim 2.64 \times 10^{17} \text{ cm}^{-3}$ ) that was chosen arbitrary and was calculated as  ${\sim}123~\text{ns}$  (at  $V_G$ =1.9 V),  $\sim$ 67.5 ns (V<sub>G</sub>=2.7 V), and  $\sim$ 21.8 ns (V<sub>G</sub> =3.6 V) for the ZnO nanowire FETs with dielectric thicknesses of 21.2, 49.6, and 78.3 nm, respectively, as shown in Fig. 4(b) (left axis). As the dielectric thickness decreased, both transconductance and capacitance increased. However, the transconductance increased dominantly, resulting in the increase of the mobility which was found to be  $\sim 127, \sim 106$ , and  $\sim 41.7 \text{ cm}^2/\text{V}$  s for 21.2, 49.6, and 78.3 nm dielectric layer thicknesses, respectively, as shown in Fig. 4(b) (right axis). Note that Bhowmick  $et al.^{21}$  theoretically predicted an increase in transconductance as decreasing the gate oxide thickness for silicon nanowire FETs.

# **IV. CONCLUSIONS**

In conclusion, we investigated the electrical characteristics of ZnO nanowire FETs with high-k Al<sub>2</sub>O<sub>3</sub> dielectrics of different thickness. For MOS structure with  $Al_2O_3$  dielectrics, the leakage current was reduced as compared with conventional SiO<sub>2</sub> gate oxides, which was characterized by the transition of DT to FN tunneling. For ZnO nanowire FETs, as the thickness of the  $Al_2O_3$  dielectric layer was reduced, the electrical conductance, transconductance, and mobility increased, and the threshold voltage shifted to the negative bias direction.

#### ACKNOWLEDGMENTS

This work was supported by the Proton Accelerator User, the National Research Laboratory (NRL) Program, the National Core Research Center (NCRC) grant, and the World Class University (WCU) program by the Korean Ministry of Education, Science and Technology (MEST) and the Program of Integrated Molecular Systems at GIST.

- <sup>1</sup>H.-S. Philip Wong, Solid-State Electron. 49, 755 (2005).

- <sup>2</sup>G. D. Wilk, R. M. Wallace, and J. M. Anthony, J. Appl. Phys. **89**, 5243 (2001).

- <sup>3</sup>J. Robertson, Eur. Phys. J.: Appl. Phys. 28, 265 (2004).

- <sup>4</sup>H. Wong and H. Iwai, Microelectron. Eng. **83**, 1867 (2006), and references therein.

- <sup>5</sup>M. D. Groner, J. W. Elam, F. H. Fabreguette, and S. M. George, Thin Solid Films **413**, 186 (2002).

- <sup>6</sup>W. Lu and C. M. Lieber, J. Phys. D **39**, R387 (2006).

- <sup>7</sup>J. C. Fisher and I. Giaever, J. Appl. Phys. **32**, 172 (1961).

- <sup>8</sup>A. Javey, H. Kim, M. Brink, Q. Wang, A. Ural, J. Guo, P. McIntyre, P. McEuen, M. Lundstrom, and H. Dai, Nature Mater. 1, 241 (2002).

- <sup>9</sup>D. Yeom, K. Keem, J. Kang, D.-Y. Jeong, C. Yoon, D. Kim, and S. Kim, Nanotechnology **19**, 265202 (2008).

- <sup>10</sup>M. Lisiansky, A. Heiman, M. Kovler, A. Fenigstein, Y. Roizin, I. Levin, A. Gladkikh, M. Oksman, R. Edrei, A. Hoffman, Y. Shnieder, and T. Claasen, Appl. Phys. Lett. **89**, 153506 (2006).

- <sup>11</sup>R. F. Klie, N. D. Browning, A. R. Chowdhuri, and C. G. Takoudis, Appl. Phys. Lett. 83, 1187 (2003).

- <sup>12</sup>W. Wang, H. D. Xiong, M. D. Edelstein, D. Gundlach, J. S. Suehle, C. A. Richter, W. -K. Hong, and T. Lee, J. Appl. Phys. **101**, 044313 (2007).

- <sup>13</sup>J. R. Hauser and K. Ahmed, AIP Conf. Proc. **449**, 235 (1998).

- <sup>14</sup>J. B. Kim, D. R. Kwon, K. Chakrabarti, C. Lee, K. Y. Oh, and J. H. Lee, J. Appl. Phys. **92**, 6739 (2002).

- <sup>15</sup>S. Guha, E. Cartier, N. A. Bojarczuk, J. Bruley, L. Gignac, and J. Karasinski, J. Appl. Phys. **90**, 512 (2001).

- <sup>16</sup>M. Cho, H. B. Park, J. Park, C. S. Hwang, J.-C. Lee, S.-J. Oh, J. Jeong, K. S. Hyun, H.-S. Kang, Y.-W. Kim, and J.-H. Lee, J. Appl. Phys. **94**, 2563 (2003).

- <sup>17</sup>J. M. Beebe, B. Kim, J. W. Gadzuk, C. D. Frisbie, and J. G. Kushmerick, Phys. Rev. Lett. **97**, 026801 (2006).

- <sup>18</sup>C. Y. Ng, T. P. Chen, and C. H. Ang, Smart Mater. Struct. **15**, S39 (2006).

<sup>19</sup>N. Arora, *MOSFET Modeling For VLSI Simulation* (World Scientific, New Jersey, USA 2007), p. 175.

- <sup>20</sup>G. Jo, J. Maeng, T.-W. Kim, W.-K. Hong, M. Jo, H. Hwang, and T. Lee, Appl. Phys. Lett. **90**, 173106 (2007).

- <sup>21</sup>S. Bhowmick and K. Alam, J. Appl. Phys. **104**, 124308 (2008).