Contents lists available at ScienceDirect

## Microelectronic Engineering

journal homepage: www.elsevier.com/locate/mee

# Data retention characteristics of MANOS-type flash memory device with different metal gates at various levels of charge injection

Man Chang, Tae-Wook Kim, Joonmyoung Lee, Minseok Jo, Seonghyun Kim, Seungjae Jung, Hyejung Choi, Takhee Lee, Hyunsang Hwang \*

Department of Materials Science and Engineering, Gwangju Institute of Science and Technology, Gwangju 500-712, South Korea

#### ARTICLE INFO

Article history: Received 2 March 2009 Received in revised form 5 March 2009 Accepted 5 March 2009 Available online 13 March 2009

Keywords: MANOS Metal gate Retention Charge loss Band bending

#### ABSTRACT

We investigated the impact of charge injection and metal gates (Al and Pt) on the data retention characteristics of metal–alumina–nitride–oxide–silicon (MANOS) devices for NAND flash memory application. Through the theoretical and experimental results, the highly injected charge ( $\Delta V_{TH}$ ) could cause the band bending of Al<sub>2</sub>O<sub>3</sub>, which reduced the tunneling distance across Al<sub>2</sub>O<sub>3</sub>. Thus, the dominant charge loss path is not only toward SiO<sub>2</sub> but also toward Al<sub>2</sub>O<sub>3</sub> direction. Compared to low-metal work function ( $\Phi_M$ ), ONA stack with high- $\Phi_M$  showed better data retention characteristics, even if  $\Delta V_{TH}$  is high. This could be explained by Fermi level alignment for different  $\Phi_M$ , which results in the reduction of electric field across the Al<sub>2</sub>O<sub>3</sub> compensated by the  $\Delta \Phi_M$  ( $\Phi_{Pt} - \Phi_{Al}$ ).

© 2009 Published by Elsevier B.V.

#### 1. Introduction

The charge trap flash (CTF) memory based on the Si<sub>3</sub>N<sub>4</sub> trapping layer has been continuously developed for the implement of massive storages [1,2]. To establish the excellent program/erase (P/E) speed and retention characteristics, the variety of approaches for the modulation of device structure has been explored. First, highk top oxide (TPO) with high-metal work function ( $\Phi_{\rm M})$  and bandgap engineered (BE) bottom oxide (BTO) were utilized to enhance the P/E speed [3,4]. The adoption of high-k dielectric as a TPO has an advantage to increase the electric field across the BTO at same physical thickness [5]. Recently, it was found that CTF memory with BE-BTO exhibited better erase speed when compared to a single SiO<sub>2</sub> BTO due to higher hole current by shortening of tunneling distance [6]. Secondly, with regard to the charge loss, the charge trapping layer with deep trap energy level and large electron energy barrier height was preferred [7]. In addition, it was reported that the traps of TPO could cause the charge loss to be increased and, thus, should be minimized [6,8].

In spite of such various approaches, there are not enough studies to understand the physical mechanisms, in particular, related to the amount of charge injection ( $\Delta V_{TH}$ ) and metal gate in terms of the data retention of the CTF memory. In this study, we investigated the retention characteristics of the SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/Al<sub>2</sub>O<sub>3</sub> (ONA) stack and the SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> (ONO) stack at various levels of  $\Delta V_{TH}$  as well as the impact of metal gate on the charge loss including its P/E speed.

#### 2. Experimental method

For this study, we used ONA (=4 nm/7 nm/15 nm) stacks and ONO (=4 nm/5.5 nm/7.5 nm) stacks. Thermally grown SiO<sub>2</sub> was used for the BTO. A Si<sub>3</sub>N<sub>4</sub> layer was deposited by low-pressure chemical vapor deposition (LPCVD) on the BTO for the storage of charges. As a TPO to block the charge loss, an Al<sub>2</sub>O<sub>3</sub> layer was deposited by means of atomic layer deposition. More details regarding ONA stack formation are described in another publication [8]. For a comparison with ONO stack, we deposited a  $SiO_2$ layer by means of LPCVD. TaN and Pt were deposited by means of RF sputter for the metal electrode and capping layer, respectively. For the metal gate study, we additionally prepared ONA stacks with 20 nm-Al and 20 nm-Pt metals, respectively. Al and Pt were deposited by e-beam. Subsequently, as a capping layer, 20 nm-Pt was deposited on the metal gate. Finally, forming gas annealing was performed at 400 °C for 30 min. In our study, the approximate  $\Phi_{\rm M}$  of Al and Pt was found to be 4.2 and 5.6 eV, respectively, extracting by the flat band voltage versus the equivalent oxide thickness plot [9].

## 3. Experimental results

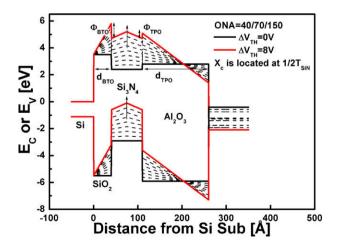

For ease of understanding about the retention state of the device, Fig. 1 shows the energy band diagrams for the ONA stack at

<sup>\*</sup> Corresponding author. Tel.: +82 62 970 2378; fax: +82 62 970 2304. *E-mail address*: hwanghs@gist.ac.kr (H. Hwang).

various levels of  $\Delta V_{\text{TH}}$ . At an initial state ( $\Delta V_{\text{TH}} = 0$  V), it is certain that the tunneling distance across the BTO ( $d_{\text{BTO}}$ ) is absolutely shorter than across the TPO ( $d_{\text{TPO}}$ ). However, as  $\Delta V_{\text{TH}}$  is gradually increased,  $d_{\text{TPO}}$  becomes more comparable to  $d_{\text{BTO}}$ . Finally, at a high level of programmed state ( $\Delta V_{\text{TH}} = 8$  V), it seems that  $d_{\text{TPO}}$  is shorter than  $d_{\text{BTO}}$ . From this figure, the amount of band bending across either BTO or TPO as a function of  $\Delta V_{\text{TH}}$  and the variation of  $d_{\text{BTO}}$ and  $d_{\text{TPO}}$  for the electrons on the Si<sub>3</sub>N<sub>4</sub> conduction band (CB) could be predicted. In here, we assumed that trap centroid ( $X_c$ ) is located at a middle of Si<sub>3</sub>N<sub>4</sub> thickness [10]. Thus, the internal electric field induced by  $\Delta V_{\text{TH}}$  is divided by [11]:

$$\Delta V_{TH} = V_{BTO} + V_{X_c} = V_{Si_3N_4 - X_c} + V_{TPO} \tag{1}$$

Further to voltage division, we can calculate both  $d_{\rm BTO}$  and  $d_{\rm TPO}$  according to Eq. (1). In this manner, we calculated the tunneling time constant ( $\tau$ ) for electrons thermally de-trapped into the Si<sub>3</sub>N<sub>4</sub> CB (1/ $e_{\rm th}$ ) and then tunneled through the oxide (1/ $e_{\rm ox}$ , BTO or TPO) using the following equation [12,13].

$$\tau = 1/e_{ox}e_{th} = 1/e_{ox,0}AT^2 \exp(-2d_{ox}\sqrt{2qm^*\Phi_{ox}}/\hbar - E_{TA}/kT)$$

(2)

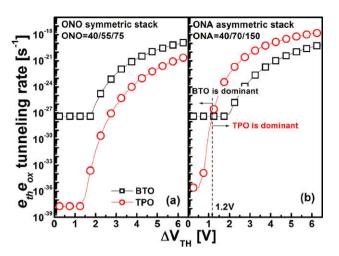

where  $e_{\text{ox},0}$ , *A* and *T* are the intrinsic time constant, temperature independent constant, and the retention temperature, respectively.  $d_{\text{ox}}$  is either  $d_{\text{BTO}}$  or  $d_{\text{TPO}}$ .  $m^*$  is the electron effective mass ( $m^*$  SiO<sub>2</sub> = 0.42,  $m^*$  Al<sub>2</sub>O<sub>3</sub> = 0.2),  $\phi_{\text{ox}}$  is the energy barrier height for electron emission ( $\Phi_{\text{Al}_2O_3}$  = 0.45 eV,  $\Phi_{\text{SiO}_2}$  = 1.05 eV),  $E_{\text{TA}}$  is the trap energy level from the Si<sub>3</sub>N<sub>4</sub> CB edge (1.4 eV in here). Compared to the  $e_{\text{th}}e_{\text{ox}}$  of ONO symmetric stack (Fig. 2a), that of ONA asymmetric stack (Fig. 2b) has a specific critical point (~1.2 V) where the transition of dominant charge loss path is expected. Regarding to charge loss path, we believe that the BTO is dominant in the  $\Delta V_{\text{TH}}$  range below 1.2 V while both the BTO and the TPO are dominant above 1.2 V.

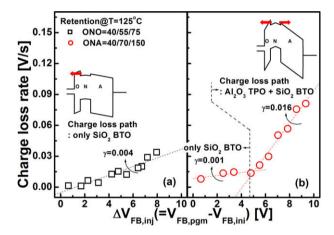

To verify the theoretical results experimentally, we estimated the charge loss rate of ONO and ONA stacks with TaN metal (Fig. 3).  $\Delta V_{\text{FB,inj}}$  indicates the difference of flat band voltage from the programmed state ( $V_{\text{FB,pgm}}$ ) to initial state ( $V_{\text{FB,ini}}$ ), that is, the amount of charge injection in MOS capacitor device. From Fig. 3, it is found that ONO stack exhibited a constant charge loss rate slope ( $\gamma$ ) of 0.004 in the whole range of charge injection, while ONA stack showed two step  $\gamma$  (1st step = 0.001, 2nd step=0.016). Based on the results of Figs. 1 and 2, a constant slope means no transition of charge loss path (1st step, toward only BTO). Contrarily, 2nd step means the addition of charge loss path toward TPO to 1st step charge loss path. Unlike our expectation, there was a large discrepancy of critical point between the calculated va-

Fig. 1. Energy band diagrams for the ONA stack structure in retention state at various levels of charge injection.

**Fig. 2.** Tunneling rates of  $e_{th}e_{ox}$  for the ONO and ONA stacks.

Fig. 3. Charge loss rate of ONO and ONA stacks with TaN metal at various levels of charge injection.

lue and the experimental one. This discrepancy arises because we still need other significant parameters for the band bending such as fixed charge [14], interfacial layer [15] and trap centroid [10,11].

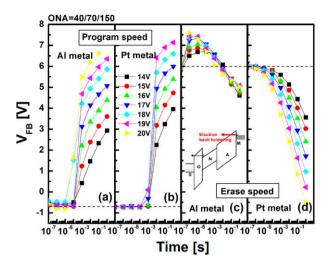

In the following, we investigated the impact of  $\Phi_{\rm M}$  on the *P*/*E* speed and data retentions at different programmed state. The ONA stack with Al and Pt metals showed similar program speed (Fig. 4a and b) although the difference of  $\Phi_M$  could give them a little change of electric field across the ONA stack. It is well known that FN tunneling is closely related to the BTO thickness and barrier height (Si/SiO<sub>2</sub>) rather than  $\Phi_M$  [3]. However, in the case of erase speed (Fig. 4c and d), they showed significantly different erase behaviors. The ONA stacks with Al metal (n-type, low- $\Phi_{\rm M}$ ) exhibited poor erase characteristics due to the electron back tunneling (EBT, inset of Fig. 4c) from the gate [3]. On the contrary, the ONA stack with Pt (p-type, high- $\Phi_{\rm M}$ ) showed a good erase behavior. It is interesting to note that this EBT seems to be more dominant at the short pulse region (<10 ms) such that this gave rise to roll-up of  $V_{\rm FB}$  shifts. This suggests that short-time erase pulses induce larger electron injection current from gate than hole current from substrate (or electron de-trapping). This related mechanism is still not completely understood.

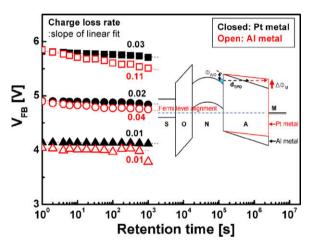

For further studies, we measured charge loss rate at different program states, as shown in Fig. 5. Charge loss rate was extracted from retention data using linear fit. At the program state of 4 V, both metal samples shows almost same charge loss rate. On the other hand, charge loss rate of Al metal sample becomes larger

**Fig. 4.** P/E speed characteristics of ONA stacks with Al and Pt metals in the pulse amplitude range from  $\pm 14$  V to  $\pm 20$  V. Inset figure illustrates the energy band diagram of erase operation and EBT.

**Fig. 5.** Charge loss rates for the ONA stacks with different  $\Phi_M$  of gate metals (Al and Pt) at different programmed state. Inset illustrates the energy band diagram with Fermi level alignment during retention characteristic.

than that of Pt metal with increasing program states. Considering the charge loss path at high level of programmed state (>4 V) (Fig. 3b), this strongly suggests that the TPO with high- $\Phi_M$  could suppress the charge loss through the TPO, indicating improved retention characteristics. This can be explained by Fermi level alignment [16]. Inset of Fig. 5 shows the energy band diagram of ONA stack with different  $\Phi_M$  of gate metals (Al and Pt) with alignment. In the case of Pt metal, the electric field across the TPO could be compensated by the  $\Delta \Phi_{\rm M}$  ( $\Phi_{\rm Pt} - \Phi_{\rm Al} = 1.4 \, {\rm eV}$ ) due to Fermi level alignment. Thus,  $d_{\rm TPO}$  of p-type metal sample might be more extended than that of n-type metal sample. However, it is noticeable that this compensation effect may not be effective at the low programmed state of 4 V, because the electric field across the TPO induced by low level of charge injection is not enough to tunnel out, even if there is  $\Delta \Phi_{\rm M}$ .

## 4. Conclusions

Charge loss behavior of ONA stack is highly dependent on  $\Delta V_{\text{TH}}$ . Particularly, for large  $\Delta V_{\text{TH}}$ , the charge loss path toward Al<sub>2</sub>O<sub>3</sub> should be considered due to the band bending effect. This result was experimentally and theoretically verified. We also investigated the impact of charge injection and metal gates (Al and Pt) on the data retention. Compared to low- $\Phi_{\text{M}}$ , ONA stack with high- $\Phi_{\text{M}}$  showed better data retention characteristics, even if  $\Delta V_{\text{TH}}$  is high. This could be explained by Fermi level alignment, which compensated the electric field across the Al<sub>2</sub>O<sub>3</sub> by the  $\Delta \Phi_{\text{M}}$  ( $\Phi_{\text{Pt}} - \Phi_{\text{Al}}$ ).

## Acknowledgements

This work was supported by the National Program for Tera-Level Nano Devices through the Ministry of Science and Technology, South Korea.

#### References

- C.-H. Lee, J. Choi, Y. Park, C. Kang, B.-I. Choi, H. Kim, H. Oh, W.-S. Lee, in: Symp. on VLSI Technology, 2008, p. 118.

- [2] R. Ohba, Y. Mitani, N. Sugiyama, S. Fujita, in: Tech. Dig. Int. Electron Dev. Meet., 2008, p. 839.

- [3] S. Jeon, J.H. Han, J.H. Lee, S. Choi, H. Hwang, C. Kim, IEEE Trans. Electron Dev. 52 (2005) 2654.

- [4] H.-T. Lue, T.-H. Hsu, S.C. Lai, Y.H. Hsiao, W.C. Peng, C.W. Liao, Y.F. Huang, S.P. Hong, M.T. Wu, F.H. Hsu, N.Z. Lien, S.Y. Wang, L.W. Yang, T. Yang, K.C. Chen, K.Y. Hsieh, R. Liu, C.Y. Lu, in: Symp. on VLSI Technology, 2008, p. 116.

- [5] C.-H. Lee, K.-C. Park, K. Kim, Appl. Phys. Lett. 87 (2005) 073510-1.

- [6] S. Choi, S.J. Baik, J.-T. Moon, in: Tech. Dig. Int. Electron Dev. Meet., 2008, p. 925.

[7] M. She, H. Takeuchi, T.-J. King, in: IEEE Proc. 20th Non-Volatile Semiconductor

- Memory Workshop (NVSMW), 2003, p. 53. [8] M. Chang, M. Hasan, S. Jung, H. Park, M. Jo, H. Choi, H. Hwang, Appl. Phys. Lett. 91 (2007) 192111.

- [9] S.M. Sze, Physics of Semiconductor Devices, second ed., Wiley, New York, p. 395.

- [10] Y. Yang, M.H. White, Solid-State Electron. 44 (2000) 949.

- [11] G. Wang, M.H. White, Solid-State Electron. 52 (2008) 1473.

- [12] T.H. Kim, J.S. Sim, J.D. Lee, H.C. Shim, B.-G. Park, Appl. Phys. Lett. 85 (2004) 660.

- [13] S.-D. Tzeng, S. Gwo, J. Appl. Phys. 100 (2006) 023711.

- [14] S. Jeon, C. Kim, Electrochem. Solid-State Lett. 9 (2006) G265.

- [15] M. Chang, Y. Ju, J. Lee, S. Jung, H. Choi, M. Jo, S. Jeon, H. Hwang, Appl. Phys. Lett. 93 (2008) 022101.

- [16] A. Furnémont, A. Cacciato, L. Breuil, M. Rosmeulen, H. Maes, K.D. Meyer, J.V. Houdt, Solid-State Electron. 52 (2008) 577.