## NANO LETTERS

2008 Vol. 8, No. 3 950-956

## Tunable Electronic Transport Characteristics of Surface-Architecture-Controlled ZnO Nanowire Field Effect Transistors

Woong-Ki Hong,† Jung Inn Sohn,‡ Dae-Kue Hwang,† Soon-Shin Kwon,† Gunho Jo,† Sunghoon Song,† Seong-Min Kim,§ Hang-Ju Ko,§ Seong-Ju Park,† Mark E. Welland,‡ and Takhee Lee\*.†

Department of Materials Science and Engineering, Gwangju Institute of Science and Technology, Gwangju 500-712, Korea, Nanoscience Centre, University of Cambridge, Cambridge CB3 0FF, United Kingdom, and Material Characterization Center, Korea Photonics Technology Institute, Gwangju 500-460, Korea

Received November 28, 2007; Revised Manuscript Received January 29, 2008

## **ABSTRACT**

Surface-architecture-controlled ZnO nanowires were grown using a vapor transport method on various ZnO buffer film coated c-plane sapphire substrates with or without Au catalysts. The ZnO nanowires that were grown showed two different types of geometric properties: corrugated ZnO nanowires having a relatively smaller diameter and a strong deep-level emission photoluminescence (PL) peak and smooth ZnO nanowires having a relatively larger diameter and a weak deep-level emission PL peak. The surface morphology and size-dependent tunable electronic transport properties of the ZnO nanowires were characterized using a nanowire field effect transistor (FET) device structure. The FETs made from smooth ZnO nanowires with a larger diameter exhibited negative threshold voltages, indicating n-channel depletion-mode behavior, whereas those made from corrugated ZnO nanowires with a smaller diameter had positive threshold voltages, indicating n-channel enhancement-mode behavior.

One-dimensional nanostructures such as semiconducting nanowires or carbon nanotubes are promising materials for future nanoelectronic device applications. Among these, ZnO nanostructures have attracted considerable attention due to their direct wide band gap (~3.4 eV), large exciton binding energy (60 meV), and potential use in versatile applications such as field effect transistors (FETs),¹ chemical and biological sensing,¹¹² light-emitting devices,³ and solar cells.⁴ Nanowire FETs are the fundamental element among these nanoelectronic device applications; thus it is essential to understand the electronic transport properties of nanowire transistors.

In particular, it is well-known that interface roughness plays an important role in electronic transport for conventional metal—oxide—semiconductor field effect transistors (MOSFETs) and thin film transistors (TFTs).<sup>5,6</sup> Similarly, the electronic transport in nanowire transistors can be

influenced by the surface morphology of nanowires associated with the interface roughness, including the presence of surface trap states at the interfaces between the nanowires and the dielectric layers of nanowire FETs. The addition, the properties of nanostructures used as building blocks for the assembly of nanoscale devices strongly depend on their size and shape. Therefore, the synthesis of surface morphology- and size-controlled nanostructures facilitates the fabrication and fundamental study of nanoscale devices with unique electrical properties.

Recently, zigzag-shaped and/or corrugated-shaped onedimensional (1D) nanostructures of GaN,<sup>10</sup> GaSe,<sup>11</sup> and ZnO<sup>12</sup> have been synthesized. For example, Zhou et al. and Nam et al. have synthesized 1D GaN nanostructures with zigzag shapes and corrugated shapes by a thermal reaction of gallium sources and ammonia, respectively, at an elevated temperature.<sup>10</sup> Also, Peng et al. have reported that GaSe nanowires exhibited a variety of morphologies including straight, zigzag, and saw-tooth shapes, which could be controlled by altering the growth temperature and time.<sup>11</sup> ZnO nanowires with corrugated shapes or zigzag shapes

<sup>\*</sup> Corresponding author. E-mail: tlee@gist.ac.kr.

<sup>†</sup> Department of Materials Science and Engineering, Gwangju Institute of Science and Technology.

<sup>\*</sup> Nanoscience Centre, University of Cambridge.

<sup>§</sup> Material Characterization Center, Korea Photonics Technology Institute.

grown using a vapor technique have also been reported.<sup>12</sup> Although many studies have been carried out on the shapecontrolled nanostructures, 10-12 such research has been focused only on the growth itself and growth mechanism as characterized by structural/optical observations. Moreover, despite many studies on charge transport in ZnO nanowires, 1b,13 the surface morphology- and size-dependent effects on the electronic transport of nanowires with corrugated shapes or zigzag shapes have rarely been reported. The surface morphology and size of nanowires are closely related to the surface states and/or surface defects; 14,15,21 thus, the electronic transport of nanowires can be strongly influenced by the surface effects due to such surface states and/or defects.<sup>7,8,16</sup> Therefore, optimum control of the density of surface states and/or defects is a crucial factor in various device applications. For example, we have previously reported that ZnO nanowire FETs with n-channel depletion-mode and enhancement-mode transistors can be realized due to the difference of surface states and/or defects induced by the surface morphology of ZnO nanowire side walls.<sup>17</sup> The realization of such nanowire transistors having different operational modes can lead to wide applications for the logic circuits.<sup>17</sup> Ultimately, ZnO nanowires must have electrical tunability by surface morphology and size control in order to achieve the potential applications of ZnO nanowire-based electronic devices.

In this Letter, we show that the density of surface states and/or defects can be experimentally controlled by the surface morphology- and size-controlled ZnO nanowires grown on various ZnO buffer film-coated c-plane sapphire (c-Al<sub>2</sub>O<sub>3</sub>) substrates. We present the tunable electronic transport characteristics of surface-architecture-controlled ZnO nanowire FETs and demonstrate that the electrical tunability is associated with the surface effects by surface states and/or defects as well as the nanowire diameter.

ZnO nanowires with smooth and corrugated surface morphology were grown on ZnO buffer film-coated c-plane sapphire substrates with or without Au catalysts by a vapor transport method. The growth of ZnO nanowires by the vapor transport method has been reported in detail elsewhere (see also the Supporting Information).<sup>18</sup> To control the surface morphology and size of the ZnO nanowires, three sets of sapphire substrates with ZnO buffer films were used: (1) an undoped ZnO film with Au catalyst (denoted as Au-ZnO film) or without Au catalyst (denoted as ZnO film), (2) a gallium-doped ZnO film with Au catalyst (denoted as Au-GZO film) or without Au catalyst (denoted as GZO film), (3) an aluminum-doped ZnO film with Au catalyst (denoted as Au-AZO film) or without Au catalyst (denoted as AZO film). Additionally, an Au-coated sapphire (denoted as Au-sapphire) substrate was also used for comparison with the ZnO buffer film-coated sapphire substrates. ZnO buffer films with approximately 1  $\mu$ m thickness were grown on the sapphire substrates by a radio frequency (rf) sputtering system using a commercially sintered ZnO target, a Ga<sub>2</sub>O<sub>3</sub> (1 wt %)-doped ZnO target, and an Al<sub>2</sub>O<sub>3</sub> (1 wt %)-doped ZnO target. The Au thin film (~3 nm) was deposited on some substrates using an e-beam evaporator to form Au catalysts as universal catalysts for the growth of onedimensional nanostructures.

The size, surface morphology, and crystal structure of the ZnO nanowires were characterized using field emission scanning electron microscopy (FESEM) and transmission electron microscopy (TEM). The photoluminescence (PL) mapping system (RPM2000 model, Accent Opt. Tech., U.K.) with a 325 nm He-Cd laser (4.6 mW) as an excitation source was used to study the optical properties of the ZnO nanowires at room temperature. In order to enable statistical descriptions of the electronic transport characteristics of surfacearchitecture-controlled ZnO nanowires, a total of 327 nanowire FET devices were fabricated and characterized (Figure 3, Figure S1 in the Supporting Information): 48 FETs of nanowires grown on Au-ZnO film, 41 FETs of nanowires grown on ZnO film, 54 FETs of nanowires grown on Au-GZO film, 55 FETs of nanowires grown on GZO film, 58 FETs of nanowires grown on Au-AZO film, 51 FETs of nanowires grown on AZO film, and 59 FETs of nanowires grown on the Au-sapphire substrate. A detailed description of the fabrication of ZnO nanowire FET devices has been reported elsewhere (see also the Supporting Information).<sup>18</sup> In particular, all the FET devices were passivated by poly(methyl methacrylate) (PMMA) to remove the influence of water or gas molecules in ambient air on ZnO nanowire FETs and to improve the FET performance by enhancing the gate-coupling effects. 17-19 The electronic transport characteristics of the ZnO nanowire FETs were investigated using a semiconductor parameter analyzer (HP4155C) at room temperature.

The TEM images of surface-architecture-controlled ZnO nanowires grown on various substrates are shown in Figure 1. The TEM images show two different types of ZnO nanowires, with a corrugated surface (Figure 1, panels a, b, c, and f) and with a smooth surface (Figure 1, panels d and e). The diameters of the ZnO nanowires were found to be  $83.6 \pm 1.4, 89.9 \pm 1.3, 85.7 \pm 1.4, 111.9 \pm 1.7, 107.7 \pm$  $1.5,88.6 \pm 2.4$ , and  $112.8 \pm 1.7$  nm for the nanowires grown on Au-ZnO film, ZnO film, Au-GZO film, GZO film, Au-AZO film, AZO film, and Au-sapphire substrates, respectively. Here, the average diameters and the error values of each type of nanowires were determined statistically from FESEM images of roughly ~100 different nanowires grown on each different type of substrates; however FESEM images were not enough to resolve the roughness of corrugated nanowires. The degree of the roughness of the corrugated nanowires could be estimated from TEM images in the following two ways: (i) the "absolute" roughness, which can be defined as the difference of the arithmetic mean values of maximum and minimum diameters of the corrugated nanowires, and (ii) the "relative" roughness, which can be defined as the absolute roughness divided by the average diameters of the corrugated nanowires. In these ways, we found the absolute roughness and relative roughness as 6.4 nm and 7.7%, 6.6 nm and 7.3%, 7 nm and 8.2%, and 5.8 nm and 6.5% for the corrugated nanowires grown on Au-ZnO film, ZnO film, Au-GZO film, and AZO film, respectively.

**Figure 1.** TEM images of the ZnO nanowires grown on various ZnO buffer film-coated c-plane sapphire substrates: undoped ZnO film (a and b), Ga-doped ZnO film (c and d), and Al-doped ZnO film (e and f) with and without Au catalysts, respectively. The scale bars are 20 nm.

As shown in Figure 1, the ZnO nanowires with relatively smaller diameters were found to have rougher surfaces than those with relatively larger diameters. The corrugated ZnO nanowires can have a larger surface area to volume ratio than smooth ZnO nanowires. These results indicate that the surface morphology and diameter size of the nanowire can be controlled by various substrates. Although the size-dependent growth mechanism of ZnO nanowires with corrugated and smooth surfaces grown on the different substrates is not yet clearly understood, we propose that ZnO nanowires with distinctive surface morphology and size can be formed due to various effects, which include nanocatalyst composition, interfacial layer, surface charge, surface roughness, surface strain, tensile stress, and Zn supersaturation variation. 11,20

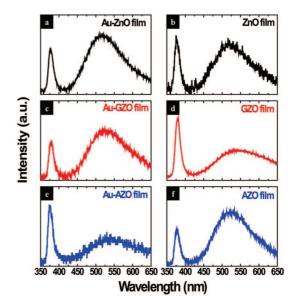

Panels a—f of Figure 2 show the PL spectra measured at room temperature for ZnO nanowires grown on various substrates. ZnO nanowires were first transferred from the growth substrates to silicon wafers, and the PL spectra were obtained from the ZnO nanowire transferred silicon wafers in order to eliminate signals coming from the ZnO buffer films themselves. The PL spectra in Figure 2 are the average values of individual signals acquired from 13 different positions within each ZnO nanowire transferred silicon wafer. As shown in Figure 2, the PL emissions of the ZnO nanowires consist of two main bands; one is the near-band-edge (NBE) excitonic related ultraviolet (UV) emission band with a peak position between 375 and 380 nm. The other is the broad deep-level (DL)-related emission (or trap-state emission) in the visible range that is attributed to the surface

**Figure 2.** Photoluminescence spectra of the ZnO nanowires grown on various substrates.

defects of the crystal. Thus, DL emission is determined by the surface states and/or the concentration of the corresponding surface defects. 14,21 Although both the corrugated and smooth types of ZnO nanowires have both UV and DL emission peaks, the UV-to-DL emission ratios  $(I_{UV}/I_{DL})$  are very different between corrugated and smooth ZnO nanowires. For the corrugated ZnO nanowires with relatively smaller diameters, the DL emission is strong and the UV emission becomes relatively weak, whereas for the smooth ZnO nanowires with relatively larger diameters, the DL emission is weak and the UV emission becomes relatively strong. Since the DL emission peak is a surface-related process, it reveals that the ZnO nanowires with large  $I_{\text{IIV}}$ /  $I_{\rm DL}$  ratios have a low density of surface states and/or defects, whereas those with small  $I_{\rm UV}/I_{\rm DL}$  ratios have a high density of surface states and/or defects. 14,21 Therefore, the luminescence of ZnO nanowires grown on various substrates is dependent on the surface morphology and the diameter size of nanowires, which play important roles in the process leading to visible emission. Although the origin of broad visible emission as typical characteristics of ZnO materials is still controversial, the surface states and/or defects are responsible for the surface morphology- and size-dependent luminescence. 14,21 These surface states and/or defects of ZnO materials introduce various defect energy levels inside the band gap of ZnO,<sup>22</sup> so that the surface effects by such surface states and/or defects influence the ZnO nanowire-based devices.

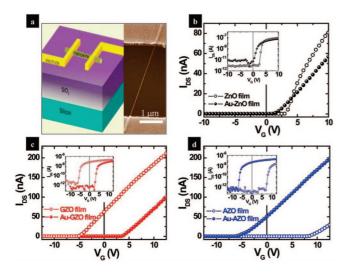

In order to study the influence of such surface states and/ or defects on the electronic transport properties of surface-architecture-controlled ZnO nanowires, we have examined the electronic transport characteristics using the nanowire FET structure. Panels b-d of Figure 3 show the representative transfer characteristics, source-drain current versus gate voltage ( $I_{DS}-V_G$ ) at a fixed source-drain voltage,  $V_{DS}=0.1$  V, of the surface-architecture-controlled ZnO nanowire FETs. The nanowires grown on different substrates exhibited

**Figure 3.** (a) Schematic diagram and SEM image of a ZnO nanowire FET. (b—d) The  $I_{\rm DS}-V_{\rm G}$  characteristics of FETs made from ZnO nanowires grown on various substrates, measured at  $V_{\rm DS}=0.1\,$  V. Labels are explained in the text. The insets show the semilogarithmic plots of  $I_{\rm DS}-V_{\rm G}$  curves with current on–off ratios as large as  $10^4-10^6$ .

different electronic transport characteristics. The FET devices made from smooth ZnO nanowires (nanowires grown on GZO and Au-AZO films; panels d and e of Figure 1) have negative threshold voltages (open symbols in Figure 3c and filled symbols in Figure 3d), indicating *n*-channel depletionmode behavior that exhibits nonzero current at the zero gate bias. In contrast, the FETs made from corrugated ZnO nanowires (nanowires grown on Au-ZnO, ZnO, Au-GZO, and AZO films, Figure 1, panels a, b, c, and f) have positive threshold voltages (Figure 3b, filled symbols in Figure 3c, and open symbols in Figure 3d), indicating n-channel enhancement-mode behavior that exhibits off-current status at zero gate bias. The insets of panels b-d of Figure 3, the  $I_{\rm DS} - V_{\rm G}$  plots on the semilogarithmic scale, display on/off current ratios as large as  $10^5 - 10^6$ . Furthermore, the effective carrier concentration can be estimated from the total charge,  $Q_{\text{tot}} = C_{\text{G}} |V_{\text{G}} - V_{\text{th}}|$  in the nanowire, where  $C_{\text{G}}$  is the gate capacitance and  $V_{\rm th}$  is the threshold voltage required to deplete the nanowire. The carrier concentration,  $n_e = Q_{tot}$  $e\pi r^2 L$ , can also be determined, where r is the nanowire radius and L ( $\sim$ 4  $\mu$ m) is the nanowire channel length. At  $V_G = 10$ V, the carrier concentrations of the representative FET devices (Figure 3, panels b-d) were estimated as 1.09 ×  $10^{18}$ ,  $7.82 \times 10^{17}$ ,  $7.68 \times 10^{17}$ ,  $1.21 \times 10^{18}$ ,  $1.26 \times 10^{18}$ , and  $1.62 \times 10^{17} \text{ cm}^{-3}$  for nanowires grown on Au–ZnO, ZnO, Au-GZO, GZO, Au-AZO, and AZO films, respectively. In addition, the transconductances  $(g_{\rm m} = {\rm d}I_{\rm DS}/{\rm d}V_{\rm G},$ slopes in  $I_{DS}$  –  $V_G$  plots in Figure 3) above threshold voltages for the corrugated nanowires are comparable with those of the smooth nanowires. As seen in Figure S4 in the Supporting Information, the transconductance does not quite depend on the nanowire diameter or nanowire roughness.

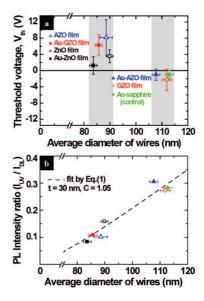

In order to investigate the practical tunability of electronic transport characteristics in the surface-architecture-controlled ZnO nanowire FETs, we statistically examined all 327 FETs

**Figure 4.** (a) Distribution of threshold voltages and (b) PL intensity  $I_{\rm UV}/I_{\rm DL}$  ratios with fitting curves as a function of the average diameter of ZnO nanowires.

of the ZnO nanowires grown on various substrates. The threshold voltages observed for all 327 FETs are summarized in Figure 4 (see also Figure S1 in the Supporting Information). As shown in Figure 4a, the corrugated ZnO nanowires have relatively smaller diameters and positive threshold voltages, whereas smooth ZnO nanowires have relatively larger diameters and negative threshold voltages. Note that the threshold voltage is defined as the gate voltage obtained by extrapolating the linear portion of the transfer characteristics  $(I_{DS}-V_G)$  from the point of maximum slope to zero drain current, in which the point of maximum slope is the point where transconductance ( $g_{\rm m} = {\rm d}I_{\rm DS}/{\rm d}V_{\rm G}$ ) is maximal.<sup>23</sup> The negative threshold voltage, exhibiting depletion-mode behavior, is attributed to delocalized electrons from shallow donors in the channel, whereas the positive threshold voltage, exhibiting enhancement-mode behavior, is attributed to deep traps in the channel or at the interface.<sup>28</sup> Therefore, the electronic transport properties of the smooth ZnO nanowires with larger diameters are quite different from those of the corrugated ZnO nanowires with smaller diameters due to the scattering or trapping of the conduction electrons at the interfaces and/or near the surface of the ZnO nanowire. In particular, corrugated ZnO nanowires with smaller diameters can have a more significant fraction of the electron depletion region in the nanowire channel due to electron traps. The results shown in Figure 4a indicate that the surface morphology and the diameter size of nanowires can have a significant effect on the electronic transport properties of nanowire-based devices.

Figure 4b shows the relationship between the  $I_{\rm UV}/I_{\rm DL}$  ratios of the PL spectra of the ZnO nanowires (obtained from Figure 2) and the nanowire diameter. Smooth ZnO nanowires with larger diameters exhibited larger  $I_{\rm UV}/I_{\rm DL}$  ratios than corrugated ZnO nanowires with smaller diameters. The PL spectra and the  $I_{\rm UV}/I_{\rm DL}$  ratios are influenced by the surface effects and the diameter size of nanowires. The  $I_{\rm UV}/I_{\rm DL}$  ratios can be fitted using the surface-recombination-layer

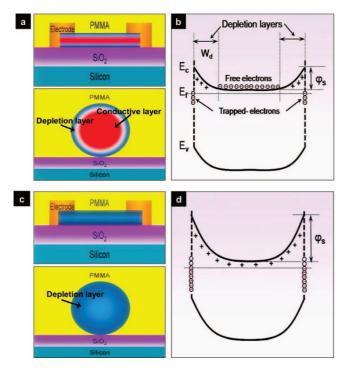

**Figure 5.** A cross-sectional view across the electrodes, ZnO nanowire, and dielectric layers (a and c) and the corresponding equilibrium energy band diagrams of nanowire FETs at  $V_{\rm G}=0$  V (b and d) for smooth ZnO nanowires (a and b) and rough ZnO nanowires (c and d).

approximation model with the following equation<sup>14</sup>

$$\frac{I_{\text{UV}}}{I_{\text{DL}}} = C \left( \frac{(D/2)^2}{2(D/2)t - t^2} - 1 \right) \tag{1}$$

where C is an approximation constant related to a collection efficiency difference at wavelengths of UV and DL peaks, D is the nanowire diameter, and t is a surface recombination thickness. 14 The thickness of the surface recombination layer (t) was assumed to be 30 nm as the previously reported value. 14,24 The optimized fitting curve obtained with eq 1 (using t = 30 nm, C = 1.05) is plotted as the dashed line in Figure 4b. This result implies that the contribution of the surface recombination to DL emission is predominant for smaller-diameter nanowires, resulting in increased surface effects. 14,21 Moreover, according to the analysis of X-ray absorption near-edge structure (XANES) spectra of the ZnO nanorods by Chiou et al.,15a the effect of surface states is enhanced when the diameter of ZnO nanorods is decreased. Therefore, tailoring the surface by controlling the surface morphology and diameter size of the nanowire plays an important role in the design and the fabrication of ZnO nanowire-based devices. Note that the difference in threshold voltage ( $\Delta V_{\text{th}}$ ) of various series of nanowire FET devices is correlated with the difference in  $I_{\rm UV}/I_{\rm DL}$  ratios ( $\Delta(I_{\rm UV}/I_{\rm DL})$ ) observed for ZnO nanowires grown on various substrates. For example,  $\{\Delta V_{\text{th}} \text{ and } \Delta (I_{\text{UV}}/I_{\text{DL}})\}$  values were found as 2.29 V and 0.075, 8.54 V and 0.164, and 9.16 V and 0.204 between the ZnO nanowires grown on the Au-ZnO and ZnO films, Au-GZO and GZO films, and Au-AZO and AZO films, respectively. As plotted in Figure S5 in the Supporting Information, the values of  $\Delta V_{\text{th}}$  increase along with  $\Delta (I_{\text{UV}}/I_{\text{DL}})$ .

Figure 5 shows cross-sectional schematics (Figure 5a,c) across the electrodes, ZnO nanowire, and dielectric layers

with the corresponding equilibrium energy band diagram (Figure 5b,d) of the ZnO nanowire FETs at  $V_G = 0$  V. Panels a and b of Figure 5 show the case for smooth ZnO nanowires, and panels c and d of Figure 5 depict the case for corrugated ZnO nanowires. For polycrystalline semiconductor materials, band bending can occur mainly due to interfacial traps at the grain boundaries, 6,25 whereas for single crystalline semiconductor materials, band bending can occur at surfaces and/or interfaces such as semiconductor/dielectrics,7 semiconductor/electrodes, 16b semiconductor/electrolytes, 26 and semiconductor/chemisorbates.<sup>27</sup> Similarly, the surface states and/or defects on single crystalline nanowires can induce trap energy levels at the interfaces, resulting in band bending due to Fermi level pinning. 8,9b,16b,c The carrier trap states at the interfaces are important in determining the operation modes of transistors.<sup>28</sup> The trapping of carrier electrons in the trap states can cause electron depletion in the channel, resulting in a gate threshold voltage shift and a conductance modulation. 13a,c,25 Correspondingly, the tunable electronic transport behavior between corrugated and smooth ZnO nanowires can be explained by considering the depletion of electron carriers due to surface band bending at the PMMA/ ZnO nanowire and/or ZnO nanowire/SiO2 interfaces as shown in Figure 5. Note that for convenience of discussion and simplification of charge transport mechanism, we assumed the uniform charge and gate potential distribution for nanowires with circular cross sections. However, the typical back-gate nanowire FET geometry is significantly influenced by the cross-sectional shapes of nanowires and whether the nanowire is embedded or not. 20a In addition, the back-gate nanowire FET geometry has the limitation in accuracy for calculating the gate-nanowire capacitance as well as the complication for the experimental extraction of transport parameters under the presence of depletion region and trap states.7,19b

To confirm depletion by surface band bending, we can compare the geometrical diameter of the nanowire with the depletion region (W) considered effective diameter, which can be estimated as  $^{1b,8,29}$

$$W = \left(\frac{2\epsilon_{\rm ZnO}\varphi_{\rm S}}{eN_{\rm D}}\right)^{1/2} \tag{2}$$

where  $\varphi_s$  is the surface barrier potential, e is the electronic charge,  $N_D$  is the doping density, and  $\epsilon_{ZnO}$  is the dielectric constant of ZnO. Then by using the depletion approximation and charge neutrality condition, <sup>25b,29</sup> the surface trap density ( $N_t$ ) can be estimated as  $N_t = 2N_DW$ . Thus, the effective diameter ( $D_{eff}$ ) of the conduction layer in the nanowire channel can be expressed as

$$D_{\rm eff} = D - \left(\frac{N_{\rm t}}{N_{\rm D}}\right) \tag{3}$$

where D is the geometrical diameter of nanowire. Therefore, by assuming that the  $N_{\rm D}=10^{17}$  /cm³,  $\epsilon_{\rm ZnO}=8.66,^{30}$   $\varphi_{\rm S}=0.3$  eV, and the nanowire diameter (D) is 100 nm, we obtain W=54 nm and  $D\leq 2W$  from eqs 2 and 3 (see also Figure S3 in the Supporting Information). This result indicates that the surface depletion can have a significant influence on the electronic transport behavior of ZnO nanowires since the

depletion width can be comparable to the diameter size of nanowire. Therefore, smooth ZnO nanowires are partially depleted under the no gate bias condition due to the smaller depletion region than the nanowire diameter (Figure 5a,b), whereas corrugated ZnO nanowires are completely depleted under the no gate bias condition (Figure 5c,d) due to the larger depletion region than the nanowire diameter. This explains why the operation mode of ZnO nanowire FETs can be controlled by the modulation of surface states and/or defects by surface morphology and size control. Consequently, the smooth ZnO nanowire FETs with large diameters can operate as the *n*-channel depletion-mode type with a partially depleted channel region due to the low density of surface trap states (Figure 5a), whereas the corrugated ZnO nanowire FETs with small diameters can operate as the n-channel enhancement-mode type with a fully depleted channel region due to the high density of surface trap states (Figure 5b) under the no gate bias condition.

In summary, we have shown that surface states and/or defects can be controlled by altering the surface architecture of the ZnO nanowires grown on various ZnO buffer film-coated sapphire substrates through the vapor transport method. We have presented the tunable electronic transport characteristics of the surface-architecture-controlled ZnO nanowire FETs and demonstrated their surface morphology-and size-dependent electrical tunability attributable to surface effects and band bending at the interfaces between the ZnO nanowire and dielectric layer.

**Acknowledgment.** This work was supported through the Proton Accelerator User Program by the Ministry of Science and Technology of Korea, the National Research Laboratory (NRL) Programs of the Korea Science and Engineering Foundation (KOSEF), and the Program for Integrated Molecular System at GIST.

**Supporting Information Available:** Descriptions of synthesis of ZnO nanowires and fabrication of ZnO nanowire FETs, statistical distribution of threshold voltages for ZnO nanowire FETs, characteristics of ZnO nanowires grown on an Au-coated sapphire substrate, depletion width and effective diameter of ZnO nanowires, and transconductance vs nanowire diameter or roughness, PL intensity ratio ( $I_{\rm UV}/I_{\rm DL}$ ) vs threshold voltage. This material is available free of charge via the Internet at http://pubs.acs.org.

## References

- (1) (a) Wang, Z. L J. Phys.: Condens. Matter 2004, 16, R829.

(b) Goldberger, J.; Sirbuly, D. J.; Law, M.; Yang, P. J. Phys. Chem. B

2005, 109, 9.

- (2) Dorfman, A.; Kumar, N.; Hahm, J. Adv. Mater. 2006, 18, 2685.

- (3) Bao, J.; Zimmler, M. A.; Capasso, F. Nano Lett. 2006, 6, 1719.

- (4) Law, M.; Greene, L. E.; Johnson, J. C.; Saykally, R.; Yang, P. D. Nat. Mater. 2005, 4, 455.

- (5) Wang, J.; Polizzi, E.; Ghosh, A.; Datta, S.; Lundstrom, M. Appl. Phys. Lett. 2005, 87, 043101.

- (6) Hastas, N. A.; Dimitriadis, C. A.; Kamarinos, G. J. Appl. Phys. 2002, 92, 4741.

- (7) (a) Dayeh, S. A.; Soci, C.; Yu, P. K. L.; Yu, E. T.; Wang, D. Appl. Phys. Lett. 2007, 90, 162112. (b) Dayeh, S. A.; Soci, C.; Yu, P. K. L.; Yu, E. T.; Wang, D. J. Vac. Sci. Technol., B 2007, 25, 1432.

- (8) Wang, D.; Chang, Y.-L.; Wang, Q.; Cao, J.; Farmer, D. B.; Gordon, R. G.; Dai, H. J. Am. Chem. Soc. 2004, 126, 11602.

- (9) (a) Lieber, C. M. Solid State Commun. 1998, 107, 607. (b) Calarco, R.; Marso, M.; Richter, T.; Akanat, A. I.; Meijers, R.; Hart, A. d.; Stoica, T.; Lüth, H. Nano Lett. 2005, 5, 981. (c) Elfström, N.; Juhasz, R.; Sychugov, I.; Engfeldt, T.; Karlstrom, A. E.; Linnros, J. Nano Lett. 2007, 7, 2608. (d) Chen, C. Q.; Shi, Y.; Zhang, Y. S.; Zhu, J.; Yan, Y. J. Phys. Rev. Lett. 2006, 96, 075505. (e) Hsu, Y.-J.; Lu, S.-Y.; Lin, Y.-F Small 2006, 2, 268.

- (10) (a) Zhou, X. T.; Sham, T. K.; Shan, Y. Y.; Duan, X. F.; Lee, S. T.; Rosenberg, R. A. J. Appl. Phys. 2005, 97, 104315. (b) Nam, C. Y.; Tham, D.; Fischer, J. E. Appl. Phys. Lett. 2004, 85, 5676.

- (11) Peng, H.; Meister, S.; Chan, C. K.; Zhang, X. F.; Cui, Y. Nano Lett. 2007, 7, 199.

- (12) (a) Xu, L.; Su, Y.; Chen, Y.; Xiao, H.; Zhu, L.; Zhou, Q.; Li, S. J. Phys. Chem. B 2006, 110, 6637. (b) Fan, H. J.; Fuhrmann, B.; Scholz, R.; Himcinschi, C.; Berger, A.; Leipner, H.; Dadgar, A.; Krost, A.; Christiansen, S.; Gösele, U.; Zacharias, M. Nanotechnology 2006, 17, S231. (c) Glushenkov, A. M.; Zhang, H. Z.; Zou, J.; Lu, G. Q.; Chen, Y. Nanotechnology 2007, 18, 175604. (d) Hughes, W. L.; Wang, Z. L. J. Am. Chem. Soc. 2004, 126, 6703.

- (13) (a) Ju, S.; Lee, K.; Yoon, M.-H.; Facchetti, A.; Marks, T. J.; Janes, D. B *Nanotechnology* 2007, 18, 155201. (b) Chang, P.-C.; Fan, Z.; Chien, C. J.; Stichtenoth, D.; Ronning, C.; Lu, J. G. Appl. Phys. Lett. 2006, 89, 133113. (c) Fan, Z.; Wang, D.; Chang, P.-C.; Tseng, W.-Y.; Lu, J. G Appl. Phys. Lett. 2004, 85, 5923. (d) Li, Q. H.; Wan, Q.; Liang, Y. X.; Wang, T. H. Appl. Phys. Lett. 2004, 84, 4556. (e) Soci, C.; Zhang, A.; Xiang, B.; Dayeh, S. A.; Aplin, D. P. R.; Park, J.; Bao, X. Y.; Lo, Y. H.; Wang, D. Nano Lett. 2007, 7, 1003.

- (14) Shalish, I.; Temkin, H.; Narayanamurti, V. Phys. Rev. B 2004, 69, 245401.

- (15) (a) Chiou, J. W.; Kumar, K. P. K.; Jan, J. C.; Tsai, H. M.; Bao, C. W.; Pong, W. F.; Chien, F. Z.; Tsai, M.-H.; Hong, I.-H.; Klauser, R.; Lee, J. F.; Wu, J. J.; Liu, S. C. Appl. Phys. Lett. 2004, 85, 3220. (b) Ozawa, K.; Sawada, K.; Shirotori, Y.; Edamoto, K. Phys. Rev. B 2003, 68, 125417.

- (16) (a) Hanrath, T.; Korgel, B. A. J. Phys. Chem. B 2005, 109, 5518. (b) Liao, Z.-M.; Liu, K.-J.; Zhang, J.-M.; Xu, J.; YuD. -P., Phys. Lett. A 2007, 367, 207. (c) Jones, F; Léonard, F.; Talin, A. A.; Bell, N. S J. Appl. Phys. 2007, 102, 014305.

- (17) Hong, W.-K.; Hwang, D.-K.; Park, I.-K.; Jo, G.; Song, S.; Park, S.-J.; Lee, T.; Kim, B.-J.; Stach, E. A. Appl. Phys. Lett. 2007, 90, 243103.

- (18) (a) Hong, W.-K.; Kim, B.-J.; Kim, T.-W.; Jo, G.; Song, S.; Kwon, S.-S.; Yoon, A.; Stach, E. A.; Lee, T. Colloids Surf., A 2008, 313–314, 378.

- (19) (a) Wunnicke, O. Appl. Phys. Lett. 2006, 89, 083102. (b) Khanal, D. R.; Wu, J. Nano Lett. 2007, 7, 2778.

- (20) (a) Park, D. J.; Lee, J. Y.; Kim, D. C.; Mohanta, S. K.; Cho, H. K. Appl. Phys. Lett. 2007, 91, 143115. (b) Park, S.-H.; Han, S.-W. J. Nanosci. Nanotechnol. 2007, 7, 2526. (c) Park, S.-H.; Seo, S.-Y.; Kim, S.-H.; Han, S.-W. Appl. Phys. Lett. 2006, 88, 251903. (d) Cong, G. W.; Wei, H. Y.; Zhang, P. F.; Wu, J. J.; Liu, X. L.; Jia, C. M.; Hu, W. G.; Zhu, Q. S.; Wang, Z. G. Appl. Phys. Lett. 2005, 87, 231903. (e) Chen, Y.; Ko; H. -J.; Hong, S.-K.; Yao, T.; Segawa, Y. Appl. Phys. Lett. 2002, 80, 1358. (f) Kumar, R. T. R.; McGlynn, E.; McLoughlin, C.; Chakrabarti, S.; Smith, R. C.; Carey, J. D.; Mosnier, J. P.; Henry, M. O. Nanotechnology 2007, 18, 215704.

- (21) (a) Djurišić, A. B.; Choy, W. C. H.; Roy, V. A. L.; Leung, Y. H.; Kwong, C. Y.; Cheah, K. W.; Rao, T. K. G.; Chan, W. K.; Lui, H. F.; Surya, C. Adv. Funct. Mater. 2004, 14, 856. (b) Djurišić, A. B.; Leung, Y. H. Small 2006, 2, 944. (c) Zhou, X.; Kuang, Q.; Jiang, Z.-Y.; Xie, Z.-X.; Xu, T.; Huang, R.-B.; Zheng, L.-S. J. Phys. Chem. C 2007, 111, 12091. (d) Pan, N.; Wang, X. P.; Li, M.; Li, F. Q.; Hou, J. G. J. Phys. Chem. C 2007, 111, 17265.

- (22) (a) Lin, B.; Fu, Z.; Jia, Y. Appl. Phys. Lett. 2001, 79, 943. (b) Kohan, A. F.; Ceder, G.; Morgan, D. Phys. Rev. B 2000, 61, 15019. (c) Oh, D. C.; Suzuki, T.; Kim, J. J.; Makino, H.; Hanada, T.; Cho, M. W.; Yao, T. Appl. Phys. Lett. 2005, 86, 032909. (d) Auret, F. D.; Goodman, S. A.; Legodi, M. J.; Meyer, W. E.; Look, D. C. Appl. Phys. Lett. 2002, 80, 1340.

- (23) Arora, N. MOSFET models for VLSI circuit simulation; Springer-Verlag: Wien and New York, 1993.

- (24) Wang, D.; Seo, H. W.; Tin, C.-C.; Bozack, M. J.; Williams, J. R.; Park, M.; Sathitsuksanoh, N.; Cheng, A.-j.; Tzeng, Y. H. J. Appl. Phys. 2006, 99, 113509.

- (25) (a) Ikeda, H. J. Appl. Phys. 2002, 91, 4637. (b) Hossain, F. M.; Nishii, J.; Takagi, S.; Ohtomo, A.; Fukumura, T.; Fujioka, H.; Ohno, H.; Koinuma, H.; Kawasaki, M. J. Appl. Phys. 2003, 94, 7768. (c) Yoon, Y.; Lin, J.; Pearton, S. J.; Guo, J. J. Appl. Phys. 2007, 101, 024301.

- (26) Mora-Seró, I.; Fabregat-Santiago, F.; Denier, B.; Bisquert, J.; Tena-Zaera, R.; Elias, J.; Lévy-Clément, C. Appl. Phys. Lett. 2006, 89, 203117.

- (27) Kolmakov, A.; Moskovits, M. Annu. Rev. Mater. Res. 2004, 34, 151.

- (28) Dehuff, N. L.; Kettenring, E. S.; Hong, D.; Chiang, H. Q.; Wager, J. F.; Hoffman, R. L.; Park, C.-H.; Keszler, D. A. J. Appl. Phys. 2005, 97, 064505.

- (29) (a) Yu, P. Y.; Cardona, M. Fundamentals of Semiconducotors: Physics and materials properties; Springer-Verlag: Berlin, 2001. (b) Taur, Y.; Ning, T. H. Fundamentals of Modern VLSI Devices; Cambridge University Press: Cambridge, 1998.

- (30) Fan, Z.; Lu, J. G. J. Nanosci. Nanotechnol. 2005, 5, 1561.

NL0731116